Home » Discover the CHERI security technology » CHERI Products » Arm Morello

Start developing next-generation hardware security with this CHERI board today.

Arm Morello is a platform developed by Arm in collaboration with the University of Cambridge as part of the UK government’s Digital Security by Design (DSbD) programme. It integrates the CHERI (Capability Hardware Enhanced RISC Instructions) technology into an advanced processor architecture that builds security directly into the hardware and addresses the root causes of many long-standing software vulnerabilities.

CHERI redefines how processors manage memory and enforce access control – you can learn about the technology on this page. The CHERI Alliance’s mission is to accelerate adoption of this open technology and is really glad to be able to now offer the chance to developers to work with this platform.

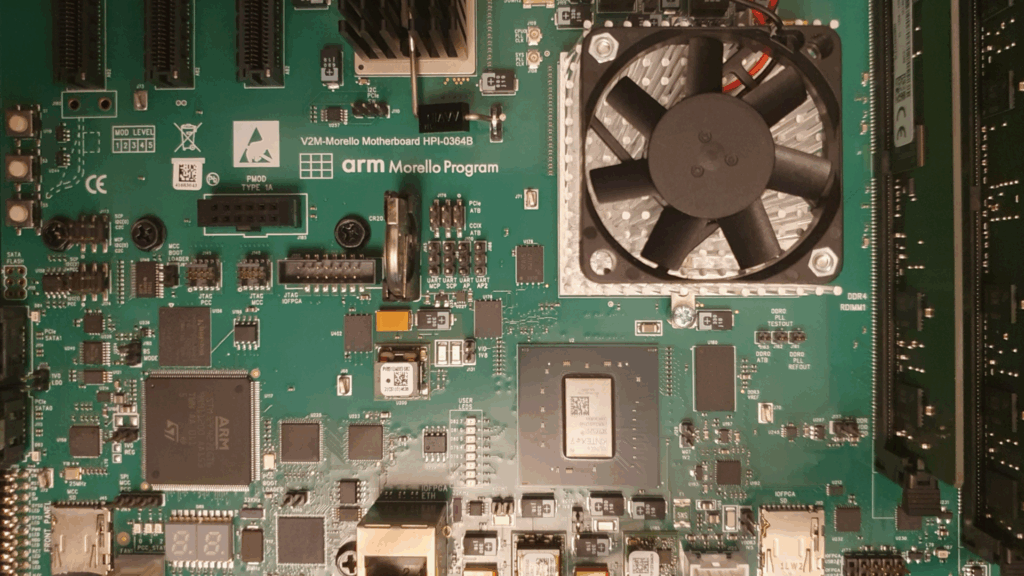

At the core of the platform is the Morello System-on-Chip (SoC), which combines a high-performance ARMv8-A processor with CHERI extensions. The accompanying Morello board provides a complete environment for developing and testing secure-by-design software components. Its software stack includes Morello Linux and an adapted LLVM/Clang toolchain, allowing developers to use familiar tools while building applications that make direct use of CHERI’s hardware capabilities.

Morello represents a major step in the industrialisation of capability-based security. By embedding protection directly in the processor, it supports the development of safer operating systems, browsers, IoT devices and cloud platforms, reducing reliance on software-only defences. This hardware foundation lays the groundwork for a new generation of computing systems that are inherently more resilient.

Through the Morello programme, the CHERI Alliance, Arm and its partners are helping industry adopt CHERI technology and plan future product integration. Morello provides a platform where organisations can build, test and validate capability-based security approaches that will shape the next wave of secure computing.

The CHERI Alliance is now distributing Arm Morello boards. These boards will be loaned to you for your projects. Since there is a very limited supply, we focus on use-cases that will help CHERI progress forward. Please describe what you want to do if you receive a board.

The team who allocates Morello boards needs to be selective to loan them to people who will use them with the maximum impact, so we have some advice to ensure that your application is successful: